talk: Energy Efficient and High Performance Architectures for DSP and Communication Applications

EE Graduate Seminar

Energy Efficient and High Performance Architectures

for DSP and Communication Applications

Tinoosh Mohsenin, PhD

Assistant Professor of Computer Engineering

CSEE Dept/UMBC

11:30am-12:45pm, 9 March 2012, ITE 231

Many emerging and future communication applications require a significant amount of high throughput data processing and operate with decreasing power budgets. This need for greater energy efficiency and improved performance of electronic devices demands co-optimization of algorithms, architectures, and implementations. This talk presents several design projects that illustrate the cross-domain optimization.

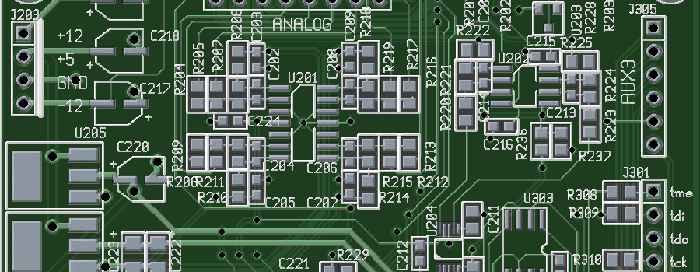

The design of System-on-Chip (SoC) blocks becomes increasingly sophisticated with emergent communication standards that have large real-time computational requirements. Two such algorithms, Low Density Parity Check (LDPC) decoding and Compressive Sensing (CS), have received significant attention. LDPC decoding is an error correction technique which has shown superior error correction performance and has been adopted by several recent communication standards. Compressive sensing is a revolutionary technique which reduces the amount of data collected during acquisition and allows sparse signals and images to be recovered from very few samples compared to the traditional Nyquist sampling. While both LDPC decoding and compressive sampling have several advantages, they require high computational intensive algorithms which typically suffer from high power consumption and low clock rates. This talk presents novel algorithms and architectures to address these challenges.

As future communication systems demand increasing flexibility and performance within a limited power budget, multi-core and many-core chip architectures have become a promising solution. The design and implementation of a many-core platform capable of performing DSP applications is presented. The low power and low area core processors are connected through a hierarchical network structure. The network protocol includes contention resolution for high data traffic between cores. The result is a platform with higher performance and lower power consumption than a traditional DSP with the ease of programmability lacking in an ASIC. Early post place and route results from a standard-cell design gives processor areas of 0.078 mm2 each using TSMCs 65 nm.

Dr. Mohsenin received the B.S. degree in electrical engineering from the Sharif University of Technology, Iran and the M.S. and PhD degrees in electrical and computer engineering from Rice University and University of California Davis in 2004 and 2010, respectively. In 2011, she joined the Department of Computer Science and Electrical Engineering at the University of Maryland Baltimore County where she is currently an Assistant Professor. Dr. Mohsenin's research interests lie in the areas of high performance and energy-efficiency in programmable and special purpose processors. She is the director of the Energy Efficient High Performance Computing (EEPC) Lab, where she leads projects in architecture, hardware, software tools, and applications for VLSI computation with an emphasis on DSP workloads. Dr. Mohsenin has been consultant to early stage technology companies and currently serves as a member of the Technical Program Committees of the IEEE Biomedical Circuits & Systems Conference (BioCAS), the Life Science Systems and Applications Workshop (LiSSA), and IEEE Women in Circuits and Systems (WiCAS).

Host: Prof. Joel M. Morris

Posted: March 6, 2012, 11:20 PM